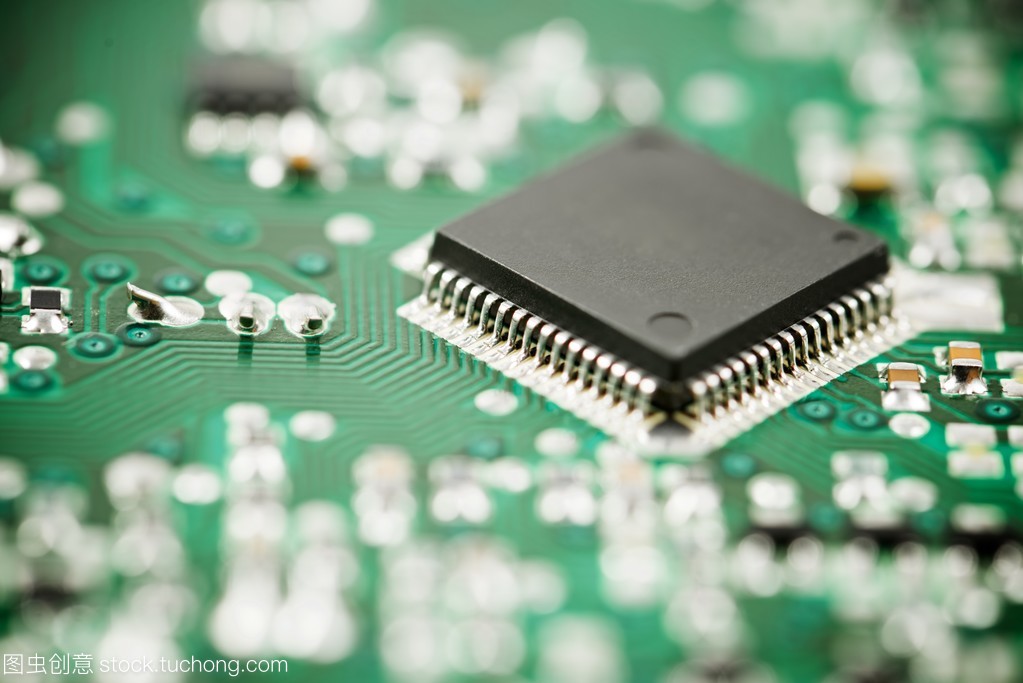

集成電路(IC)是現(xiàn)代電子設(shè)備的心臟,其性能、功耗和成本從根本上決定了電子產(chǎn)品的競爭力。而這一切的起點,便是集成電路設(shè)計視圖——一套貫穿芯片誕生全生命周期的、多層次、多角度的設(shè)計與服務(wù)藍圖。它不僅定義了芯片的物理形態(tài)與功能,更構(gòu)建了從概念到量產(chǎn)的全方位服務(wù)體系。

集成電路設(shè)計視圖是一個分層、抽象的設(shè)計過程體系,通常從高層到低層包括:

- 系統(tǒng)架構(gòu)視圖:這是最高層次的抽象,定義芯片的整體功能、性能指標、模塊劃分以及與外部的接口。它關(guān)注的是“做什么”,而非“如何做”。

- 行為/算法視圖:使用硬件描述語言(如Verilog、VHDL)或高級綜合工具,將架構(gòu)轉(zhuǎn)化為可執(zhí)行、可仿真的寄存器傳輸級(RTL)代碼。此視圖精確描述了數(shù)據(jù)在寄存器間的流動與變換。

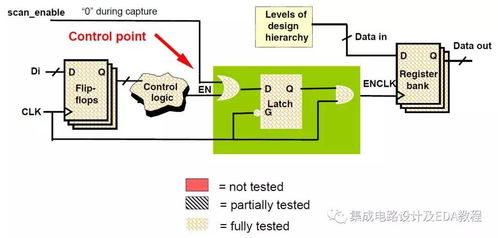

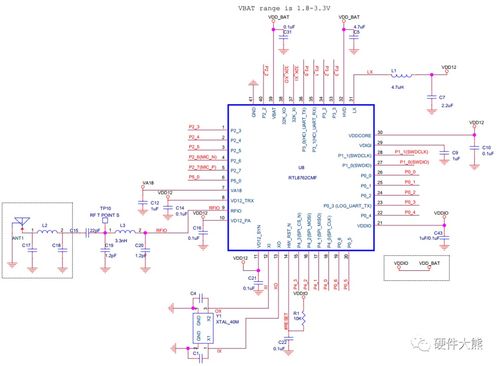

- 邏輯/門級視圖:通過邏輯綜合,將RTL代碼映射到目標工藝庫的標準邏輯門(如與門、或門、觸發(fā)器等)及宏單元上,形成門級網(wǎng)表。此視圖關(guān)注邏輯功能的正確性和時序。

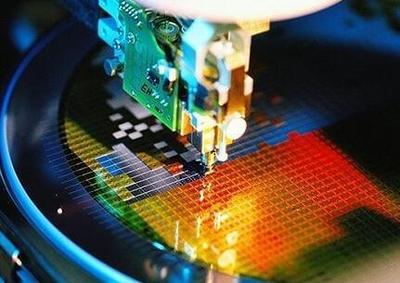

- 物理設(shè)計視圖:這是將邏輯網(wǎng)表轉(zhuǎn)化為物理版圖的過程,包括布局(規(guī)劃芯片上模塊的位置)、布線(連接各模塊和單元的金屬連線)、時鐘樹綜合、電源規(guī)劃等。此視圖決定了芯片的最終面積、性能和可制造性。

- 驗證與簽核視圖:貫穿所有層級,通過仿真、形式驗證、靜態(tài)時序分析、物理驗證等手段,確保設(shè)計在功能、時序、功耗和物理規(guī)則上完全正確,達到可交付制造的“簽核”標準。

集成電路芯片設(shè)計及服務(wù):從視圖到交付

基于上述設(shè)計視圖,專業(yè)的集成電路設(shè)計服務(wù)已發(fā)展為一個涵蓋全流程的產(chǎn)業(yè)生態(tài),主要包括:

- IP核設(shè)計與授權(quán):提供經(jīng)過驗證的、可復(fù)用的功能模塊(如CPU核、接口IP、存儲器等),大幅縮短設(shè)計周期。這是設(shè)計視圖的模塊化資產(chǎn)。

- 前端設(shè)計服務(wù):涵蓋從規(guī)格定義、架構(gòu)探索、RTL編碼到功能驗證的全過程,聚焦于芯片的邏輯功能實現(xiàn)。

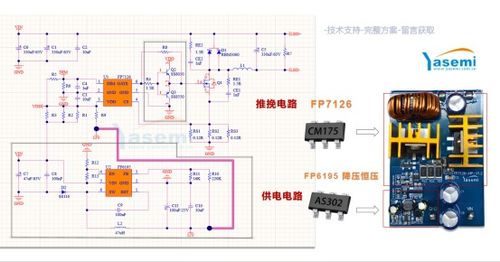

- 后端設(shè)計服務(wù):專注于物理實現(xiàn),包括邏輯綜合、物理實現(xiàn)、時序/功耗/信號完整性分析及簽核,確保設(shè)計可成功流片。

- 設(shè)計驗證與測試服務(wù):提供從系統(tǒng)級到門級的全方位驗證解決方案,以及量產(chǎn)測試方案開發(fā),保證芯片功能與質(zhì)量。

- 全流程Turnkey服務(wù):為客戶提供從概念到GDSII交付(甚至到量產(chǎn)管理)的一站式芯片設(shè)計解決方案,客戶只需定義需求與規(guī)格。

- 先進工藝與封裝協(xié)同設(shè)計服務(wù):隨著工藝演進至納米級及先進封裝(如2.5D/3D IC)的普及,服務(wù)范疇擴展到跨工藝節(jié)點的設(shè)計優(yōu)化和多芯片/芯粒的協(xié)同設(shè)計與集成。

****

集成電路設(shè)計視圖是指導(dǎo)芯片從無形創(chuàng)意走向有形硅片的科學(xué)方法與技術(shù)路標。而圍繞這些視圖展開的專業(yè)設(shè)計服務(wù),則將復(fù)雜的設(shè)計工程轉(zhuǎn)化為可靠、高效的市場化過程。在萬物互聯(lián)與智能計算的時代,掌握先進的設(shè)計視圖方法論并依托強大的設(shè)計服務(wù)生態(tài),已成為企業(yè)駕馭芯片創(chuàng)新、贏得市場競爭的關(guān)鍵所在。設(shè)計與服務(wù)深度融合,共同推動著集成電路產(chǎn)業(yè)不斷突破物理與技術(shù)的邊界。